# **Agilent E2960B Series**

Hardware and Probing Guide

#### Notices

© Agilent Technologies, Inc. 2008-2009

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

#### **Print History**

E2960-97001, October 2009

E2960-97000, September 2009

#### **Trademarks**

Windows 2000®, Windows XP®, and Microsoft .NET Framework 1.1® are U.S. registered trademarks of Microsoft Corporation.

#### **Manual Part Number**

E2960-97001

#### **Edition**

Sixth edition, October 2009

Available in electronic format only

Agilent Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

#### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

#### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

#### **Safety Notices**

#### CAUTION

A **CAUTION** notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a **CAUTION** notice until the indicated conditions are fully understood and met.

#### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

#### **Safety Summary**

| Safety Symbols |               |                                                                                                                                                                                                       |

|----------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| on Instruments | Safety Symbol | Description                                                                                                                                                                                           |

|                |               | Indicates warning or caution. If you see this symbol on a product, you must<br>refer to the manuals for specific Warning or Caution information to avoid<br>personal injury or damage to the product. |

|                | rth,          | Frame or chassis ground terminal. Typically connects to the equipment's metal frame.                                                                                                                  |

|                |               | Indicates hazardous voltages and potential for electrical shock.                                                                                                                                      |

|                | À             | Indicates that antistatic precautions should be taken.                                                                                                                                                |

|                |               | Indicates hot surface. Please do not touch.                                                                                                                                                           |

|                |               |                                                                                                                                                                                                       |

**General Safety Precautions** The following general safety precautions must be observed during all phases of operation of this instrument. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the instrument.

Indicates laser radiation turned on.

Safety requirements.

Agilent Technologies Inc. assumes no liability for the customer's failure to comply with these requirements.

CSA is the Canadian certification mark to demonstrate compliance with the

ISM GRP-1A classification according to the international EMC standard. ICES/NMB-001 compliance marking to the Canadian EMC standard.

CE compliance marking to the EU Safety and EMC Directives.

Before operation, review the instrument and manual for safety markings and instructions. You must follow these to ensure safe operation and to maintain the instrument in safe condition.

**General** This product is a Safety Class 1 instrument (provided with a protective earth terminal). The protective features of this product may be impaired if it is used in a manner not specified in the operation instructions.

All Light Emitting Diodes (LEDs) used in this product are Class 1 LEDs as per IEC 60825-1.

**Environment** Conditions This instrument is intended for indoor use in an installation category II, pollution degree 2 environment. It is designed to operate at a maximum relative humidity of 95% and at altitudes of up to 2000 meters.

**S₽ ∘**

Refer to the specifications tables for the ac mains voltage requirements and ambient operating temperature range.

**Before Applying Power** Verify that all safety precautions are taken. The power cable inlet of the instrument serves as a device to disconnect from the mains in case of hazard. The instrument must be positioned so that the operator can easily access the power cable inlet. When the instrument is rack mounted the rack must be provided with an easily accessible mains switch.

**Ground the Instrument** To minimize shock hazard, the instrument chassis and cover must be connected to an electrical protective earth ground. The instrument must be connected to the ac power mains through a grounded power cable, with the ground wire firmly connected to an electrical ground (safety ground) at the power outlet. Any interruption of the protective (grounding) conductor or disconnection of the protective earth terminal will cause a potential shock hazard that could result in personal injury.

Do Not Operate in Do not operate the instrument in the presence of flammable gases or fumes. Atmosphere

Do Not Remove<br/>the Instrument<br/>CoverOperating personnel must not remove instrument covers. Component<br/>replacement and internal adjustments must be made only by qualified<br/>personnel.

Instruments that appear damaged or defective should be made inoperative and secured against unintended operation until they can be repaired by qualified service personnel.

Environmental Information

#### Contents

Safety Summary 3

- 1 N5306A I/O Module

- 2 N5322A Extended Interface Module

- **3 N5309A Exerciser Card and Extension Card**

N5309A Exerciser Card 16

N5309-66417 Exerciser Extension Card 20

- 4 N5323A Jammer Card

- 5 N5315 Solid Slot Interposer Card

- 6 N5316A Backplane Board for PCIe

#### 7 Soft Touch Midbus Probes

Midbus 2.0 (Full Size) Probes 40 **Overview and Configuration Support** 41 Installation Instructions 41 Characteristics 42 Mechanical Design Considerations for Midbus 2.0 Probes 43 Electrical Design Considerations for the Midbus 2.0 Probes 50 N5328A Half Size Midbus Probe 62 Setting Up the Probe 64 Footprint Pinout of the Probe 64 **Mechanical Dimensions** 65 **Electrical Design Considerations for Midbus Probes** 69 Midbus Placement Within System Topology 69 Load Model 71 **Reference Clock Probe** 72 Mechanical Design Considerations for the Reference Clock Probe 72 Electrical Design Considerations for the Reference Clock Probe 74

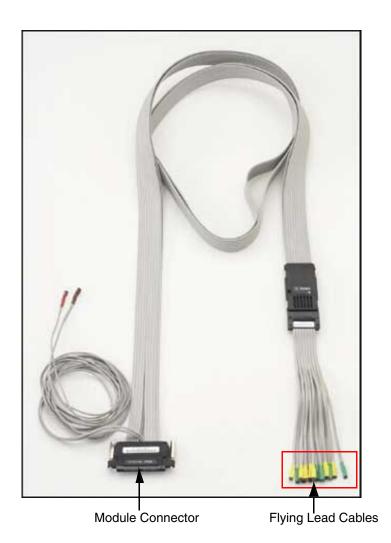

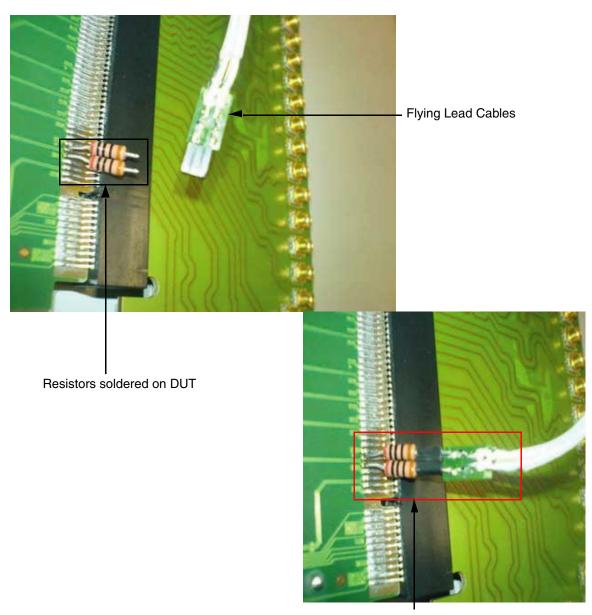

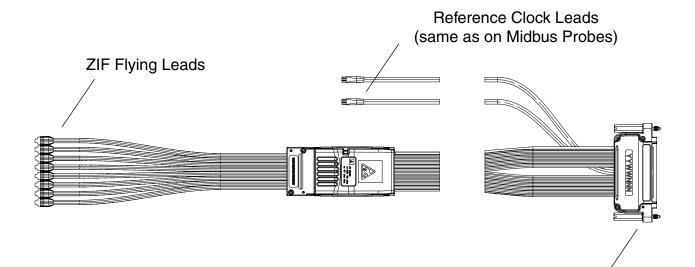

#### 8 N4241F Flying Lead Probe

Resistor Dimensions 78 Lane Mapping 80 Important Points About Using N4241F 81

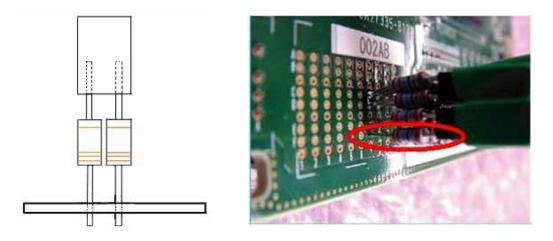

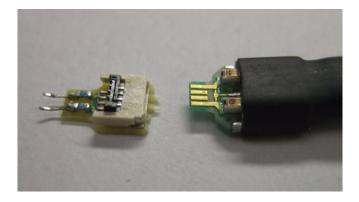

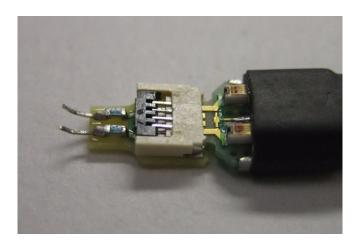

#### 9 N4241Z ZIF Flying Lead Probe

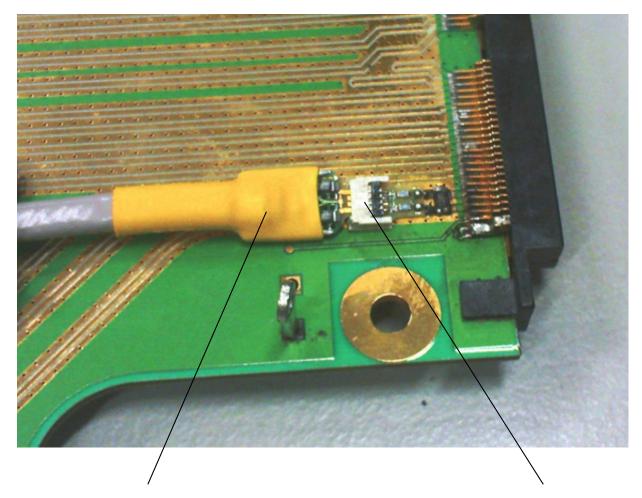

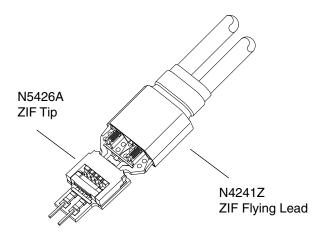

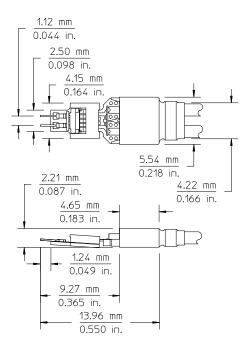

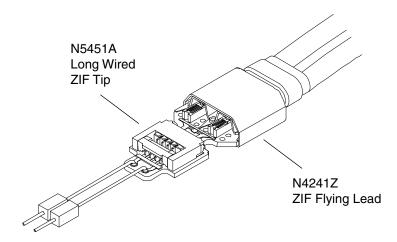

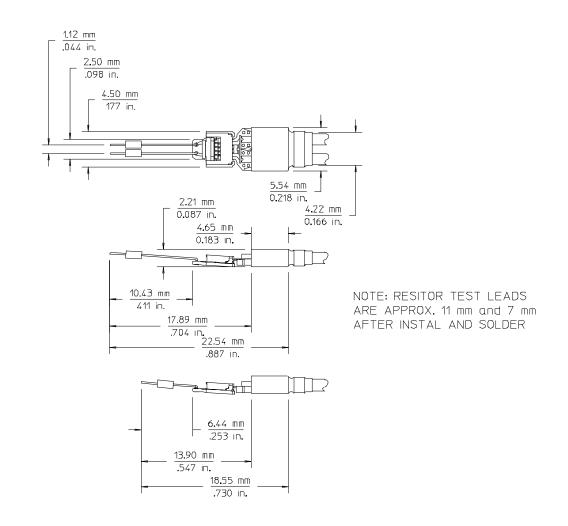

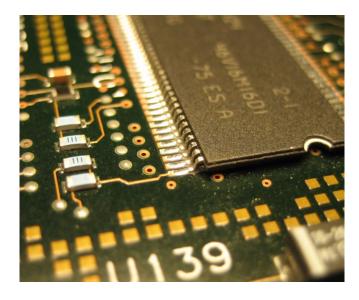

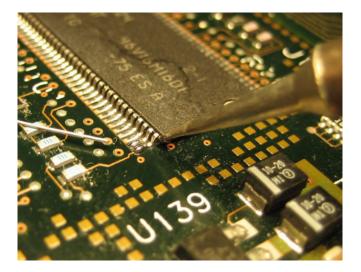

N5426A ZIF Tip 86 87 N5426A ZIF Tip Dimensions N5451A Long Wired ZIF Tip 88 N5451A Long Wired ZIF Tip Dimensions 89 Trimming Log Wired ZIF Tip Resistor Leads 89 Soldering Resistors to Long Wired ZIF Tips 91 Breaking Off Long Wired ZIF Tips from Packaging Strip 94 **ZIF Flying Lead Connection to DUT** 95 ZIF Tip Connection to Flying Lead 95 Soldering the ZIF Tip or Long Wired ZIF Tip into a DUT 96 Lane Mapping 102 Important Points About Using N4241Z 103

Index

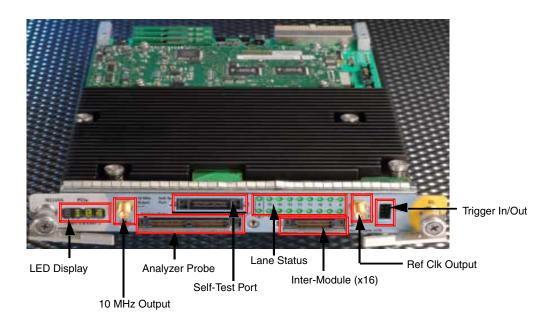

This chapter provides information on the N5306A I/O module used for PCIe.

Figure 1 N5306A I/O Module

As shown in Figure 1, the N5306A I/O module has the following components:

- **LED Display** This component is used to display the diagnostic information when fatal faults are discovered, and to indicate progress during the bootstrap. If everything is working properly, then this component displays the module number, such as 103.

- 10 MHz Output— This component is a reference clock, which is used for generating timestamps in Protocol Analyzer. This component delievers 10 MHz output.

- **Analyzer Probe** This component is used to connect the midbus probe *module connector* with N5306A and N5307A (slot interposer card).

For complete information on midbus probe, refer to Agilent Soft Touch Midbus Probe, User's Guide.

**Agilent Technologies**

For information on plugging midbus probe module connector with N5306A Analyzer Probe, refer to *Agilent System Protocol Tester*, *Installation Guide*.

- Self-Test Port— This component is a loopback board, and is used to connect the midbus probe *tip* with N5306A. The one side of this loopback board has a retainer for the probe, and the other side has the connector for the self-test port. To verify if N5306A I/O module and midbus probe are working properly, plug in this loopback board into the self-test port and then watch the lane status.

- Lane Status— This component has 18 LED bullets that displays the status of the lane by using different colored bullets. Two bullets, labelled **A** and **B**, indicate global status information. Different colors used to indicate global status information are:

- Grey This colored bullet means system is not configured.

- **Red** This colored bullet means the speed is not detected or the system is not configured.

- Yellow This colored bullet represents speed of 2.5 Gb/s

- Green This colored bullet represents speed of 5 Gb/s.

Other 16 LED bullets, labelled **0** to **15**, indicate the status of each lane. These bullets are:

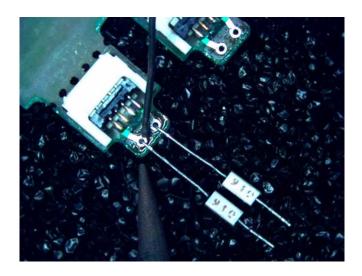

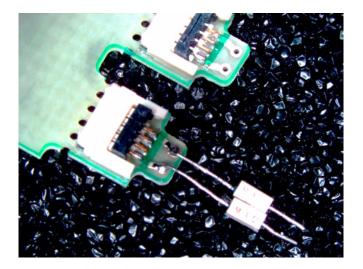

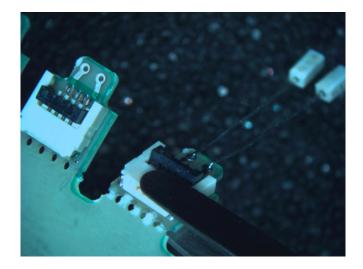

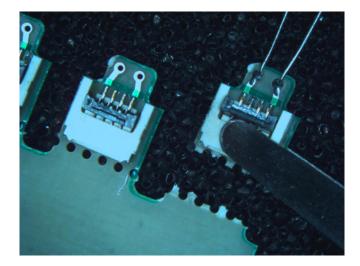

- **Red** This colored bullets means that there are no signals or the lane is electrically idle.

- **Orange** This colored bullet marks the presence of invalid signals on the lane.

- **Green** This colored bullet means that the data on the lane is deskewed.

- **Blinking Green** This colored bullet means that the data on the lane is skewed. It corresponds to *yellow* in the Port Overview pane in the Protocol Analyzer GUI.

- **Grey** This colored bullet means that the lane is not configured. For example, if you are using x4 link width, then first four bullets of the lane would be green and rest of the bullets would be grey colored bullets.

- Inter-Module (x16)— This component is used to share information with another N5306A I/O module in the same chassis. The features of this component are not yet supported by the System Protocol Tester platform.

- **Ref Clk Output** This components is a *reference clock*, which N5306A use to process the data internally. This components delivers 100 MHz output.

- **Trigger In/Out** This component is used to listen to external trigger in from a different device or send external trigger out to another device.

The following figure shows meaning of the pins of the Trigger In/Out component.

| GND      | $\bigcirc$ | $\bigcirc$ | GND     |

|----------|------------|------------|---------|

| Trig Out | $\bigcirc$ | $\bigcirc$ | Trig In |

| 10MHz    | $\bigcirc$ |            |         |

Figure 2 Trigger In/Out Pins

The following are some important points about the Trigger In/Out component:

- The outputs circuitry is designed to work into open in order to fit to the LA input that is typically in the K-ohms range.

- Maximum trigger input voltage should not exceed 3.3 V.

- Trigger Out and 10 MHz Out have nominal output level of 2.0 V after 20 ns minimum pulse width.

- Minimum Trigger In duration is  $\sim 20$  ns.

NOTE

Use trigger cable to send or receive external trigger in and out events.

WARNING

Do not directly touch any component on the I/O module. It may be hot.

#### CAUTION

Components on the I/O module are sensitive to the static electricity. Therefore, take necessary anti-static precautions, such as wear a grounded wrist strap, to minimize the possibility of electrostatic damage.

#### 1 N5306A I/O Module

Agilent E2960B Series Hardware and Probing Guide

2

### **N5322A Extended Interface Module**

This chapter provides information on the N5322A extended interface module used for PCIe.

The N5322A extended interface module is used with the N5306A module to capture the traffic of DUTs that use PCIe power management (L0s, L1, L2/L3).

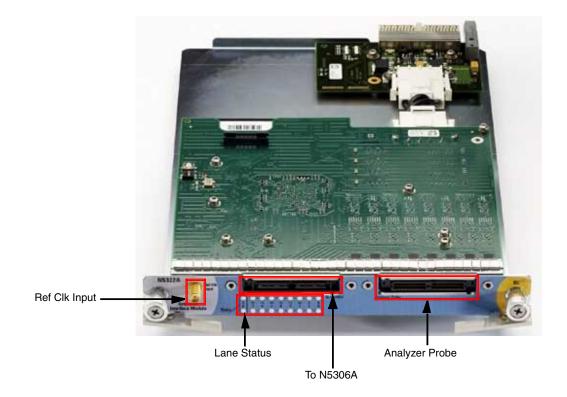

The following figure shows the N5322A extended interface module.

Figure 3 N5322A Extended Interface Module

As shown in the above figure, the N5322A module has the following components:

• **Ref Clk Input**— This component is used as an alternate 100 MHz reference clock input.

- **Analyzer Probe** This component is used to connect the N5322A module with the following probe types:

- N4241A Straight

- N4242A Swizzled

- N4243A Split Cable

- N5315A Solid Slot Interposer

- N5317A PCIe Gen1 Probe Connection Cable

- N4241F Flying Leads

- **To N5306A** This component is used to connect N5322A with N5306A using the Extended Interface Module interconnect cable.

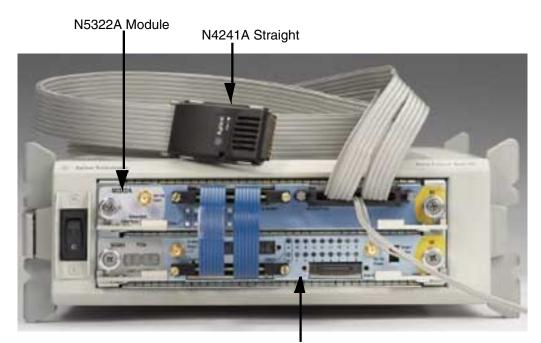

The following figure shows how you can use N5322A and N5306A modules, and a probe type together.

N5306A Module

Figure 4 N5322A paired with N5306A

NOTE

N5322A and N5306A modules should be used as a pair. That is:

- Use 1 N5306A and 1 N5322A for a x8 setup.

- Use 2 N5306A and 2 N5322A for a x16 setup.

- Lane Status— This component has 18 LEDs that display the status of the lane by using different colors. Two LEDs, labelled **A** and **B**, indicate global status information. Different colors used to indicate global status information are:

- **Green** This colored LED means that N5322A and N5306A modules are connected, the Port Overview pane in Protocol Analyzer is showing *Connected*, and also the check box for N5322A in the Hardware Setup dialog box is *selected*.

- **Yellow** This colored LED means that N5322A and N5306A modules are connected, the Port Overview pane in Protocol Analyzer is also showing *Connected*, but the check box for N5322A in the Hardware Setup dialog box is *not selected*.

- **Red** This colored LED means that N5322A is not connected with N5306A.

Other 16 LEDs, labelled **0** to **15**, indicate the status of each lane. These LEDs are:

- **Green** This colored LED means that the lane is not in electrical idle state.

- **Grey** This colored LED means that the lane is not configured. For example, if you are using x4 link width, then first four bullets of the lane would be green and rest of the bullets would be grey colored bullets.

- **Red** This colored LED means there are no signals or the lane is electrically idle.

#### WARNING Do not directly touch any component on the N5322A module. It may be hot.

#### CAUTION

Components on the N5322A module are sensitive to the static electricity. Therefore, take necessary anti-static precautions, such as wear a grounded wrist strap, to minimize the possibility of electrostatic damage.

#### 2 N5322A Extended Interface Module

Agilent E2960B Series Hardware and Probing Guide

3

# N5309A Exerciser Card and Extension Card

N5309A Exerciser Card 16 N5309-66417 Exerciser Extension Card 20

This chapter provides information on the N5309A exerciser card and the N5309-66417 exerciser extension card used for PCIe.

#### **3** N5309A Exerciser Card and Extension Card

#### N5309A Exerciser Card

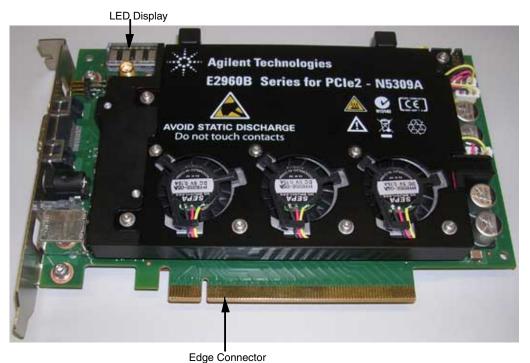

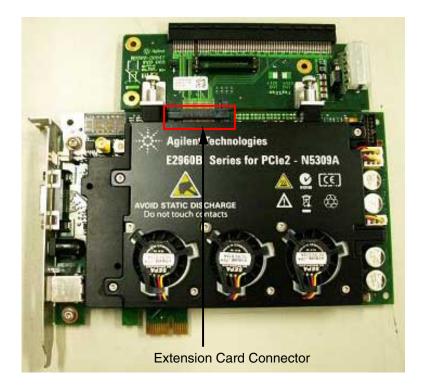

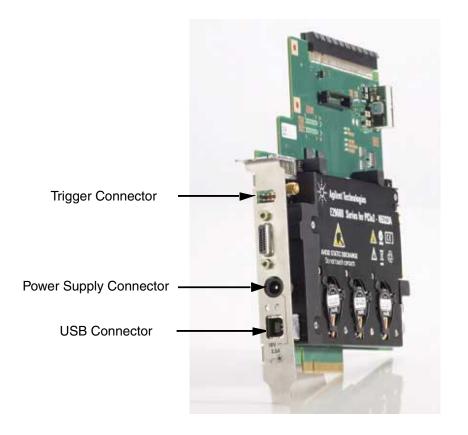

The following figure displays the N5309A exerciser card.

•

Figure 5 N5309A Exerciser Card

Components of the N5309A exerciser card are described below:

- **Ref Clk Input** This component can be used as an alternative 100 MHz reference clock input.

- **LED Display** This component displays the module number, such as *module number 10003*, to which N5309A is configured. The module number displayed here scrolls horizontally from right to left.

- **Status LEDs (on board)** This component has the following LEDs to display the status information.

Figure 6 N5309A Exerciser card - Status LEDs

- First 16 LEDs displays the status of the link.

- One LED, separately highlighted on the right, shows the power status of the board.

- Last three LEDs shows the power status of DUT.

- Edge Connector– This component is used to connect N5308A with a PCIe Connector on the backplane board, or with a system.

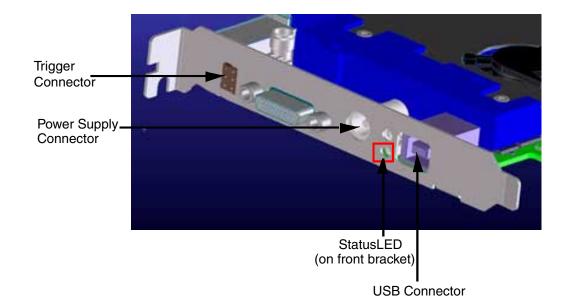

- **Trigger Connector** This component is a six-pin header, and is used to connect the trigger cable (N5306-61604) to enable triggering between Protocol Exerciser and Protocol Analyzer. In this scenario, the other end of the trigger cable is plugged into the trigger connector of the Protocol Analyzer module.

You can also use this connector for cross-triggering with other instruments, such as Logic Analyzer.

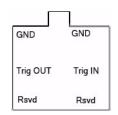

The following figure shows the meaning of the pins in the Trigger Connector component:

| GND      | GND     |

|----------|---------|

| Trig OUT | Trig IN |

| Rsvd     | Rsvd    |

Figure 7 Trigger Connector Pins

• **Power Supply Connector**— This component is used to connect N5309A with the external power supply.

Use the power supply delivered with N5309A only.

- **Status LED (on front bracket)** This LED represents the following different states:

- *No light* state means there is no link up.

- Green light means there is a link up at the Gen2 speed.

- Blinking green light means there is a link up at the Gen1 speed.

- USB Connector- This component is used to connect N5309A with the controller PC using the USB cable.

The following figure shows the Trigger Connector, Power Supply Connector, Link Status LED, and USB Connector components.

NOTE

The N5309A exerciser card also has the Extension Card Connector component at its top, which is used to connect the Exerciser Extension Card with N5309A. For more information on this component and exerciser extension card, refer to "N5309-66417 Exerciser Extension Card" on page 20.

For more information on the N5309A exerciser card, refer to:

• Agilent Protocol Exerciser, User's Guide

# WARNINGDo not directly touch any component on the N5309A exerciser card. It may be hot.CAUTIONComponents on the N5309A exerciser card are sensitive to the static electricity.<br/>Therefore, take necessary anti-static precautions, such as wear a grounded wrist<br/>strap, to minimize the possibility of electrostatic damage.

#### N5309-66417 Exerciser Extension Card

This chapter provides information on the N5309-66417 exerciser extension card used with the N5309A exerciser card for PCIe.

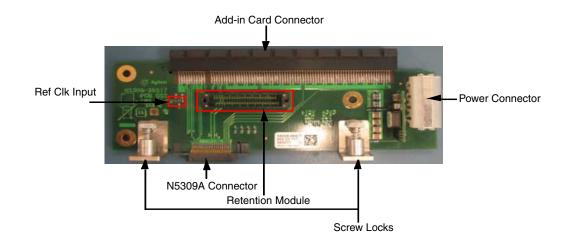

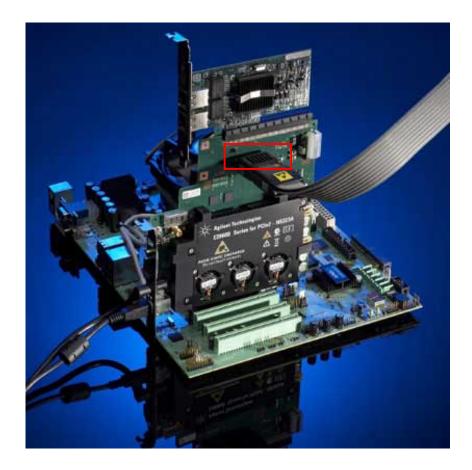

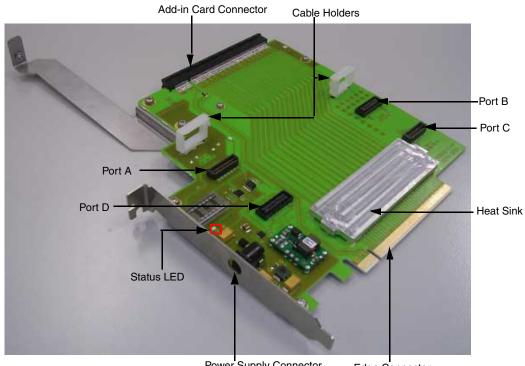

The following figure displays the N5309-66417 exerciser extension card.

Figure 9 N5309-66417 Exerciser Extension Card

Components of the N5309-66417 exerciser extension card are described below:

- **Ref Clk Input** This component can be used as an alternative 100 MHz reference clock input.

- Add-in Card Connector— This component is used to connect any add-in PCIe card at the top of N5309-66417.

- **Retention Module** This component is used to connect the midbus probe, which is then used for capturing traffic between the N5309A exerciser card and the add-in card.

- **Power Connector** This component is used to provide power supply to an add-in card, which is hooked on the N5309-66417 card.

- N5309A Connector— This component is used to connect the N5309-66417 card with the N5309A exerciser card.

To connect the two cards:

- **a** Insert the N5309A Connector component into the *Extension Card Connector* component of the N5309A card.

- **b** Tighten the *screw locks* of the N5309-66417 card to tightly align it with the N5309A card.

The following figure shows the N5309-66417 card connected with the N5309A card.

Figure 10 N5309-66417 connected with N5309A

**NOTE** The N5309-66417 exerciser extension card supports linkup only on the x1 link width.

# WARNING Do not directly touch any component on the N5309-66417 exerciser extension card. It may be hot.

**CAUTION** CAUTION Components on the N5309-66417 exerciser extension card are sensitive to the static electricity. Therefore, take necessary anti-static precautions, such as wear a grounded wrist strap, to minimize the possibility of electrostatic damage.

#### **3** N5309A Exerciser Card and Extension Card

This chapter provides information on the N5323A jammer card used for PCIe.

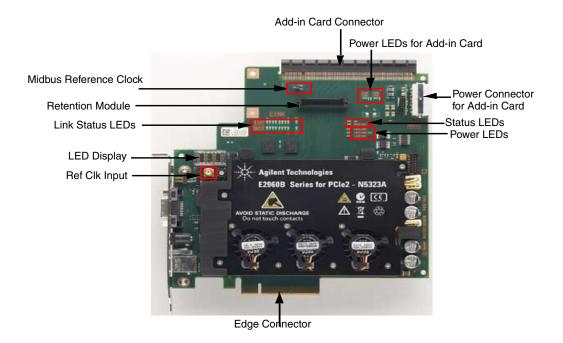

The following figure displays the N5323A Jammer card.

Figure 11 N5323A Jammer Card

Components of the N5323A jammer card are described below:

- **Ref Clk Input** This component can be used as an alternative 100 MHz reference clock input.

- LED Display– This component displays the following messages:

- *Module number* (such as module number 10003) to which N5323A is configured. The module number displayed here scrolls horizontally from right to left.

- Serial number of the board, when you open the Update GUI tool from Start > Programs > Agilent N2X > PCIE Jammer 71. Release.

- *FPPR* when the firmware is being programmed.

- *FWPR* when the firmware is programmed, and the board requires a power cycle.

- **Retention Module** This component is used to connect the midbus probe to the N5323A jammer card, which allows midbus probe to be used for capturing traffic between N5323A and the add-in card.

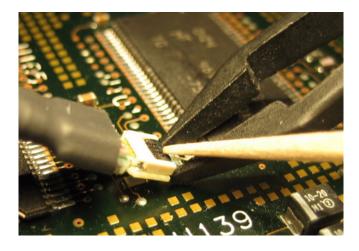

Figure 12 Midbus probe plugged into the retention module

• Midbus Reference Clock— This component can be used to connect the reference clock to the midbus probe.

NOTE

For information on midbus probe, refer to *Agilent Soft Touch Midbus Probe, User's Guide* and *Agilent System Protocol Tester, Installation Guide*.

• **Power Connector for add-in card**— This component is used to provide power supply to the add-in card, which is hooked on the N5323A jammer card.

- **Power LEDs for Add- in Card** This component has two LEDs marked as +*3V3 TOP* and +*12V TOP* displaying the status of the PCIe power to the add-in card.

- Edge Connector— This component is used to connect N5323A with a PCIe Connector on the backplane board, or with a system.

- Add-in Card Connector— This component is used to connect any add-in PCIe card at the top of N5323A.

- Link Status LEDs— This component has the following LEDs to display the PCIe link status information.

The upper row (labeled TOP) displays the status of the *link to add-in-card*, and the lower row (labelled *BOT*) displays the status of the *link to system* or *backplane*.

The link status LEDs (labelled ST) represent the following states:

- *No light* state means there is no link up.

- Green light means there is a link up at the Gen2 speed.

- Blinking green light means there is a link up at the Gen1 speed.

- **Status LEDs** This component has two LEDs marked as *HB* and *FPGA RDY* displaying the status of the board.

Flashing HB LED shows that the micro controller is running, and FPGA RDY shows that the FPGA image is loaded and ready.

- **Power LEDs** This component has three LEDs marked as +3V3 BOT, +3V3 BOT AUX, and +12V BOT displaying the status of the PCIe power supplies from the system or backplane.

- **Trigger Connector** This component is a six-pin header, and is used to connect the trigger cable (N5306-61604) to enable triggering between Jammer and Protocol Analyzer. In this scenario, the other end of the trigger cable is plugged into the trigger connector of the Protocol Analyzer module.

You can also use this connector for cross-triggering with other instruments, such as Logic Analyzer.

The following figure shows the meaning of the pins in the Trigger Connector component:

Figure 13 Trigger Connector Pins

• **Power Supply Connector**— This component is used to connect N5323A with the external power supply.

Use the power supply delivered with N5323A only.

• USB Connector- This component is used to connect N5323A with the controller PC using the USB cable.

The following figure shows the Trigger Connector, Power Supply Connector, Link Status LED, and USB Connector components.

Figure 14 N5323A Jammer Card

# **WARNING** Do not directly touch any component on the N5323A jammer card. It may be hot.

#### CAUTION

Components on the N5323A jammer card are sensitive to the static electricity. Therefore, take necessary anti-static precautions, such as wear a grounded wrist strap, to minimize the possibility of electrostatic damage.

#### 4 N5323A Jammer Card

Agilent E2960B Series Hardware and Probing Guide

5

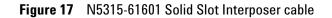

# N5315 Solid Slot Interposer Card

This chapter provides information on the N5315 solid slot interposer card used for PCIe.

The N5315 solid slot interposer card comes in four form factors: x1, x4, x8 and x16 link width.

The following figure shows the N5315 solid slot interposer card for the x16link width.

Power Supply Connector Edge Connector

Figure 15 N5315 Solid Slot Interposer Card

Components shown in the above figure are described below:

• Add-in Card Connector- This component is used to connect any add-in PCIe card at the top of N5315.

• **Edge Connector**— This component is used to connect N5315 with a PCIe Connector on the backplane board, or with a system.

This component comes with a protective foam cover to protect it from electrostatic damage.

Figure 16 Protective Foam Cover for Edge Connector

#### NOTE

Please remove the protective foam cover before using the card, and attach it again when the card is not in use.

- **Ports** N5315 has the following ports:

- Port A This port is for lanes 0-7, downstream.

- Port B This port is for lanes 8-15, downstream.

- Port C This port is for lanes 8-15, upstream.

- Port D This port is for lanes 0-7, upstream.

If you use N5315 for x8 link width, then Port B and C will not be available.

• Cable Holders— These components hold the *N5315-61601 Solid Slot Interposer* cables that connect the N5306A I/O module to the N5315 card.

The following figure shows the N5315-61601 cable.

To use this cable, plug its *Module Connector* in the *Analyzer Probe* component of the N5306A I/O module, and plug its *port connectors* in the ports of the N5315 card.

For example, a x8 setup requires one N5315-61601 cable, whereas a x16 setup requires two N5315-61601 cables.

For a x8 setup, plug the port connectors of the N5315-61601 cable into port A and D of the N5315 card, and its module connector into the Analyzer Probe component of the N5306A I/O module.

For a x16 setup, plug the port connectors of the one N5315-61601 cable into the A and D ports, and the port connectors of the second cable into the B and C ports. After this, plug the module connectors of these two cables into the Analyzer Probe components of the two N5306A I/O modules.

The following figure shows the two N5315-61601 cables connected to the ports and supported by the cable holders.

Figure 18 N5315 with Cables

|         | <ul> <li>Status LED- This component indicates whether the N5315 card is powered. It has the following two states:</li> <li>No light state means the card is not powered.</li> <li>Green light means the card is powered.</li> <li>Heat Sink- This component absorbs and dissipates heat of the card.</li> </ul> |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         |                                                                                                                                                                                                                                                                                                                 |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                 |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                 |  |  |  |

|         | • <b>Power Supply Connector</b> — This component is used to connect N5315 with the external power supply.                                                                                                                                                                                                       |  |  |  |

|         | Use the power supply delivered with N5315 only.                                                                                                                                                                                                                                                                 |  |  |  |

| NOTE    | Power supply specifications are:                                                                                                                                                                                                                                                                                |  |  |  |

|         | Input: 100 - 240 V~, 47 - 63 Hz 130 - 160 VA 1.5 A MAX                                                                                                                                                                                                                                                          |  |  |  |

|         | <b>DC Output:</b> +18 == 3.6 A 63 W MAX                                                                                                                                                                                                                                                                         |  |  |  |

| WARNING | Do not directly touch any component on the N5315 solid slot interposer card. It may be hot.                                                                                                                                                                                                                     |  |  |  |

| CAUTION | Components on the N5315 solid slot interposer card are sensitive to the static electricity. Therefore, take necessary anti-static precautions, such as wear a grounded wrist strap, to minimize the possibility of electrostatic damage.                                                                        |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                 |  |  |  |

Agilent E2960B Series Hardware and Probing Guide

# Agiler Hardv 6 N5

### N5316A Backplane Board for PCIe

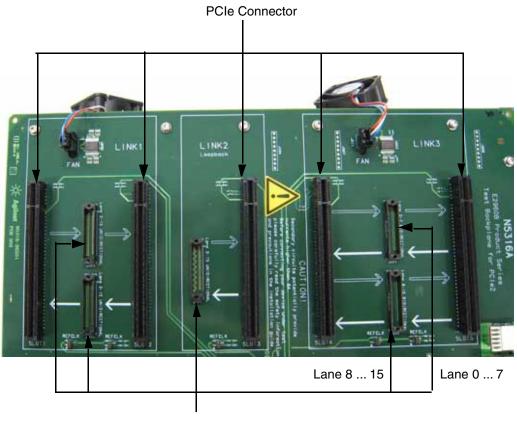

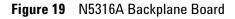

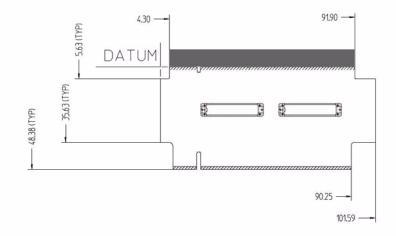

This chapter provides information on the N5316A test backplane board used for PCIe 5 Gb/s.

The following figures show the N5316A test backplane board for PCIe 5 Gb/s.

**Retention Module**

As shown in the previous figure, the N5316A backplane board has:

• Five *retention modules* for midbus probe.

• Five *PCIe connectors* for the slot interposer cards, exerciser cards, and other add- in cards (like LAN or graphic card).

As shown on the backplane board, arrows between the retention modules and PCIe connectors show the direction in which the traffic flows.

All these retention modules and PCIe connectors are arranged inside the following three sections:

- **LINK1** The retention modules in this section are unidirectional and can support link width upto x16. One direction of lanes 0...15 is routed to each retention module supporting upto x16. Using N4241A midbus probe here will display only upstreams or downstreams lanes on the I/O module. To view lanes in both directions, use the N4242A midbus probe.

- **LINK2** The retention module and PCIe connector in this section is used for loopback, wherein one PCIe card transmits packets as well as receives its own transmitted packets. Here, the midbus probe in the retention module captures the traffic flowing through loopback.

- **LINK3** The retention modules in this section are bidirectional and can support upto x8 link width. Both directions of lanes 0...7 are routed to one retention module, and lanes 8...15 to the other. Using a N4241A midbus probe, you can capture upto x8 link width on one retention module.

Lanes and directions are printed on the N5316A backplane board as well.

#### NOTE

The main application of this board is in testing an add- in card, such as a LAN or graphic card, using an exerciser card and a midbus probe. In this case, you plug the exerciser card into one PCIe connector and the add- in card into the other PCIe connector. Then, you plug the midbus probe into one of the retention module between the add- in and exerciser cards. This enables you to capture and analyze the traffic flowing between the add- in and exerciser cards.

- Five *REFCLK connectors* (reference clock connector), one for each PCIe connector. You use these connectors when you want to supply external clock feed to the PCIe connectors. In this situation, you use the Y-cable, whose tail is plugged into the external clock source and two heads into the two REFCLK connectors.

- Two *fan connectors* for the exhausts that you can use to keep the temperature of the board under control.

# **NOTE** For information on midbus probe, refer to *Agilent Midbus 2.0, User's Guide* and *Agilent System Protocol Tester, Installation Guide*.

NOTE

For information on setting up the metal sheet and exerciser card, refer to *Agilent System Protocol Tester, Installation Guide*.

The following figure shows some more components of the N5316A test backplane board for PCIe 5 Gb/s.

Figure 20 N5316A Backplane Board Components

As shown in the previous figure, the N5316A backplane board has:

• A *power switch*, which is used to switch off and on the power supply to the circuits of the board.

This power switch is given in addition to the main power switch of the board. Therefore, switching ON the main power switch is a *prerequesite* to start using the backplane board.

- A reset switch, which resets all the circuits of the board.

- Four *DIP* switches:

- One to choose between internal and external clock (*INT CLK* and *EXT CLK*).

- One to choose between disabling and enabling SSC (*SSC\_OFF* and *SSC\_ON*).

- The other two switches are not connected to the board.

- The following LEDs to show the status of above mentioned switches:

- EXT CLK- It glows when the external clock is enabled.

- INT CLK- It glows when the internal clock is enabled.

- **SSC\_ON** It glows when you shift the above mentioned switch towards the SSC\_ON label.

- A *CLOCK OUTPUT* connector, which provides a clock feed to an external device. You generally use this component when you want to synchronize an external device with the clock cycle of the backplane board.

The specifications of CLOCK OUTPUT connector are:

- Terminate into 50 Ohm

- Level Approximately 800 mVpp

- A *EXT CLK INPUT* connector, which is used to receive a clock feed for the backplane board from an external device. You generally use this component when you want to synchronize the backplane board with the clock cycle of an external device.

The specifications of EXT CLK INTPUT connector are:

- AC coupled

- Level Approximately 800 mVpp

- A *power output* connector, which has four pins: one +5V, one +12V, and two GND. Use these pins judicially to power-up an external module.

- Two 3.3V auxiliary jumpers:

- 3.3V is directly connected to the power switch, which means it turns on when you press the power switch.

- 3.3V Standby is powered on as soon as the board is powered on by the main switch.

# **WARNING** Do not directly touch any component on the N5316A backplane board. It may be hot.

#### CAUTION

Components on the N5316A backplane board are sensitive to the static electricity. Therefore, take necessary anti-static precautions, such as wear a grounded wrist strap, to minimize the possibility of electrostatic damage.

# CAUTION

During normal operations, N5316A operates safely. Nevertheless, the circuits of 3.3 V and 12 V on PCI Express connectors and 5 V on the Power Output connector are not limited and may provide currents higher than 8 A. In case of failure, for example short circuit, such a circuit presents the risk of causing fire. Therefore, to limit the energy and avoid damage, we urgently recommend implementing one of the following preventive measures:

1. Limit the circuits of your product under test with a 4A IEC fuse (5A UL fuse) at the input.

2. Operate the N5316A in a fire enclosure.

Table of electrical specification is given below:

| U— Output | Imax Output |

|-----------|-------------|

| +3.3V     | 28A         |

| +5V       | 42A         |

| +12V      | 22A         |

# 6 N5316A Backplane Board for PCIe

Agilent E2960B Series Hardware and Probing Guide

7

# Soft Touch Midbus Probes

Midbus 2.0 (Full Size) Probes 40 N5328A Half Size Midbus Probe 62 Electrical Design Considerations for Midbus Probes 69 Reference Clock Probe 72

Agilent provides midbus 2.0 (full size) probes and the N5328A half size midbus probe. The half size midbus probe can be used in situations where space constraints in a board's design prevent having a full sized probe.

Both full size and half size midbus probes connect to soft touch footprints which must be designed into the device under test (DUT).

There are electrical design considerations that apply to both the full size and half size midbus probes.

Also, both full size and half size midbus probes provide a reference clock probe for situations where it is necessary to probe the reference clock from the DUT.

# Midbus 2.0 (Full Size) Probes

This section introduces you to the Agilent midbus 2.0 probes. It also provides information on configuration support.

- "Overview and Configuration Support" on page 41

- "Installation Instructions" on page 41

- "Characteristics" on page 42

- "Mechanical Design Considerations for Midbus 2.0 Probes" on page 43

- "Electrical Design Considerations for the Midbus 2.0 Probes" on page 50

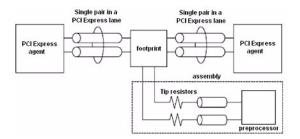

The Agilent midbus 2.0 series of probes using soft touch technology are specially designed to provide support for up to 16 channel probing solutions.

To integrate a midbus probe, a midbus probe footprint must be designed into the target board. A 3 pin header must also be designed into the target board if it is required to supply a reference clock to the protocol analyzer. This document is intended to provide information needed by platform and system design teams for integration of midbus 2.0 into their designs. It provides a mechanical and electrical solution space for Midbus Probe placement with the PCI Express bus.

Although information on PCI Express topology and specifications will be given, this document is not intended to take the place of other PCI Express design documentation. It is assumed that a design team utilizing this document for their design constraints will validate their designs through pre and post route electrical simulation and keep-out volume analysis.

#### Nomenclature • N4241A refers to midbus 2.0 straight bi-directional x8 for PCIe 5 Gb/s.

- N4242A refers to midbus 2.0 swizzled x16 for PCIe 5 Gb/s.

- N4243A refers to midbus 2.0 split x4 for PCIe 5 Gb/s.

- Midbus connection, midbus probe, and midbus footprint refer to the Agilent midbus 2.0 footprint connector (N4241A/ N4242A/ N4243A) PCI Express compression cable set.

- "channel" refers to either an upstream differential pair OR downstream differential pair for a given lane. In other words, a "channel" refers to either a transmit-differential pair OR a receive-differential pair for a given lane.

RetentionOne kit of 5 retention modules is supplied with each N4241A, N4242A,Modulesand N4243A probes.

Contact your local sales representative to order additional retention modules:

• Part Number: E2960B-RET-05

RETENTION MODULES FOR MIDBUS PROBE 2.0 - 5 PCS.

• Part Number: E2960B-RET-50 RETENTION MODULES FOR MIDBUS PROBE 2.0 - 50 PCS.

#### **Overview and Configuration Support**

Figure 21 Midbus Probe 2.0

Link Configuration

Support

The midbus 2.0 offers a number of different probing options for different applications. The platform designer has the flexibility to configure a probing solution that best meets the needs of the system. With midbus 2.0 offering upto 16 channel probing solutions, the following configurations may be made\*:

- Upstream and downstream channels of one x8 link.

- Upstream or downstream channels of one x16 link.

- Upstream or downstream channels of up to four x4, x2, or x1 links.

\*As long as the Midbus Probe placement within the system requirements are met. System designers should verify that their system requirements are supported by the midbus 2.0 by contacting Agilent Technologies directly.

Other combinations may be available. Contact Agilent Technologies for the latest support configurations.

#### **Installation Instructions**

NOTE

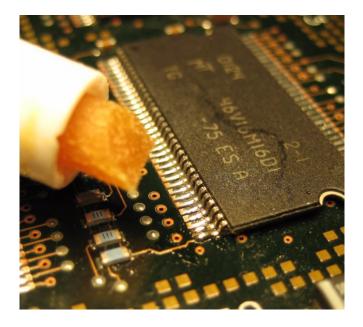

• First solder and secure the retention module onto the device under test (DUT) on two sides of the midbus probe footprint.

- Select the midbus cable (straight, swizzle or split) that best suits the design. Connect the wide connector of midbus to the Protocol Analyzer module and tighten the thumbscrews.

- Identify the white bullet on the probe label indicating pin 1 as seen in Figure 1. Align it to the pin 1 on the layout board. (While designing the layout make sure pin 1 is defined and marked.) A vertically aligned probe is shown in the Figure 2.

- Slide the probe into the retention module and gently tighten the thumbscrews located at the top of the midbus probe head. A screwdriver may be used to ensure that there is a secure connection. The thumbscrews should be tightened to a snug fit but do not over tighten.

**Figure 22** Midbus aligned over back plane

• Finally, if an external reference clock is to be supplied to protocol analyzer, connect the external clock cable (of the midbus) to the reference clock header on the target board.

# **Characteristics**

## CAUTION

Other combinations may be available. Contact Agilent Technologies for the latest support configurations.

| Probe Inputs: | Input Voltage: 25 V max or 3 V rms into 250 Ohms.                                                                                                                                                                                                                            |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature:  | Operating 0 to 40 Deg C with 200 linear feet per minute airflow.<br>Storage -40 to 70 Deg C.                                                                                                                                                                                 |

| Humidity:     | Operating 15% to 95% non condensing.                                                                                                                                                                                                                                         |

| Altitude:     | Operating: to 3000 meters (10000 ft).                                                                                                                                                                                                                                        |

| Airflow:      | For a single probe with no heat sources within 1 inch, 140 linear feet per<br>minute of air flow is required.<br>For two probes, placed side by side with minimum spacing and no other<br>heat sources within 1 inch, 200 linear feet per minute of air flow is<br>required. |

## **Mechanical Design Considerations for Midbus 2.0 Probes**

This section contains information on mechanical design of the Midbus Probe and the reference clock pin header. It also provides details on footprint dimensions, keep- out volumes, and part numbers.

- "Footprint Dimensions and Specifications" on page 43

- "Connecting the Retention Module" on page 45

- "N5311 Midbus Interposer Card" on page 48

#### **Footprint Dimensions and Specifications**

Please ensure the following pre- requisites are met for the design:

- Solder mask must not extend above the pad height for a distance of .005 inches from the pad.

- Via-in-pad is allowed if the vias are filled level with the pad or the via hole size is less that .005 inches.

- Permissible surface finishes on pads are HASL, immersion silver, or gold over nickel. The height of the pads contacted by the probe must be within +/- .007 inches of the bottom surface of the retention module.

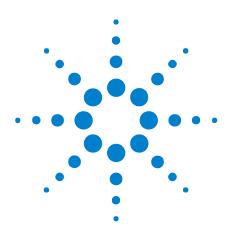

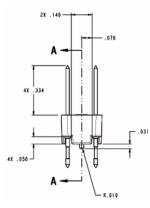

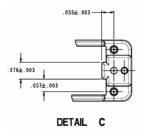

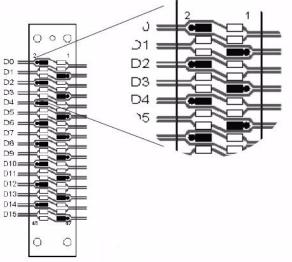

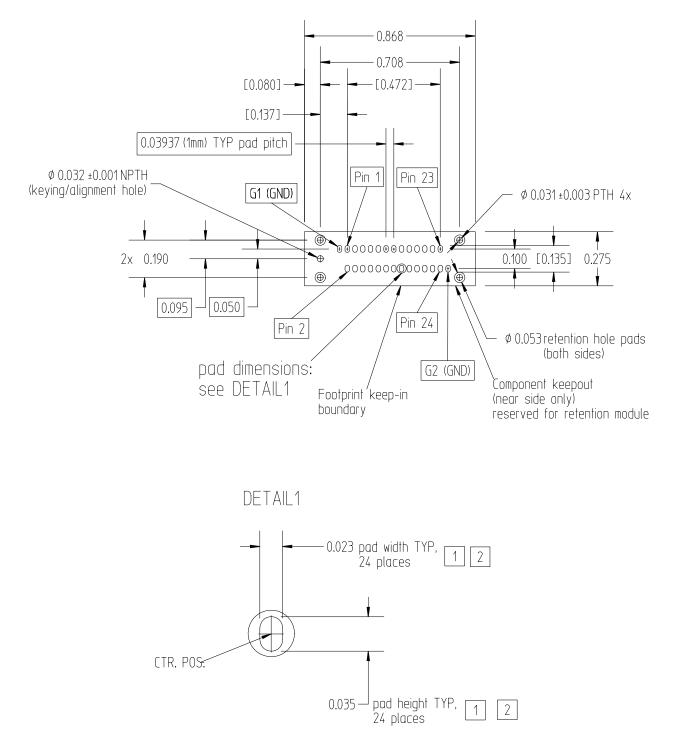

The Midbus probe 2.0 footprint, that needs to be designed into the target board can be observed in the following figure. The following figure displays the detailed layout dimensions for the footprint. Notice that the connector has 50 pins.

Figure 23 Midbus 2.0 footprint dimensions, pin numbering, and specification

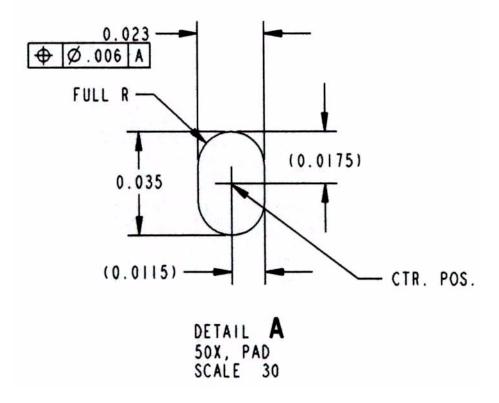

The following figure displays detailed view of a pad with geometrical information on it.

Figure 24 Detail A - detailed view of a pad.

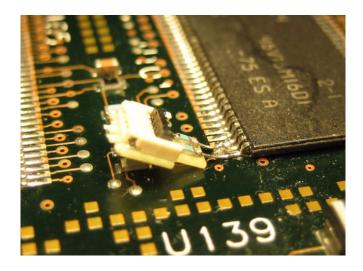

#### **Connecting the Retention Module**

The retention module helps to connect midbus probe to the device under test (DUT). To achieve this, the retention module must be soldered onto the DUT. After this is done, the probe can be easily plugged into this retention module.

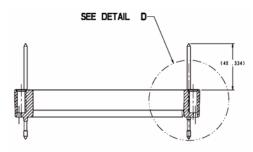

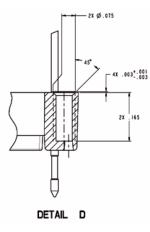

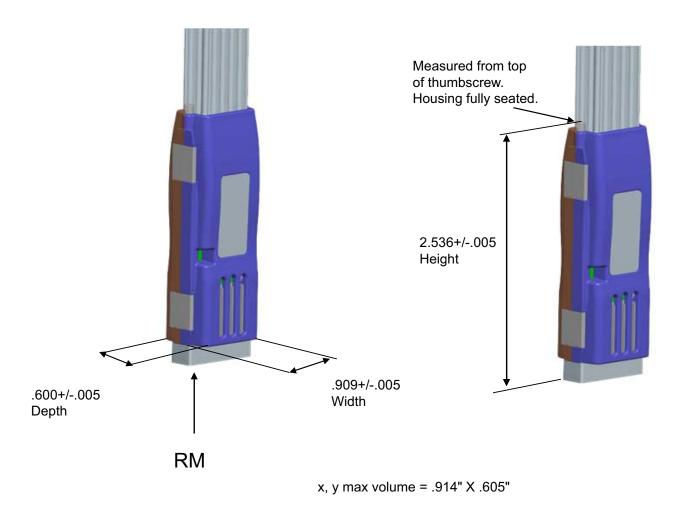

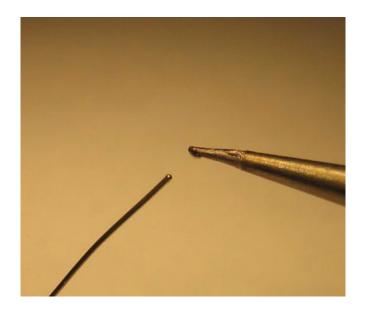

The following figure displays the dimensions of the midbus probe, which is plugged into the retention module.

Figure 25 Midbus probe plugged into the retention module

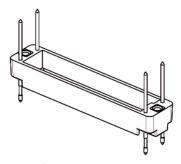

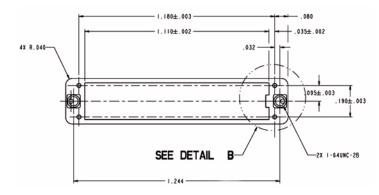

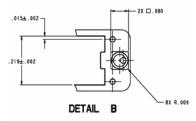

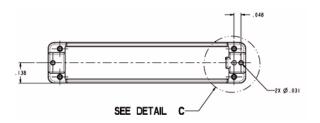

The following figure displays the retention module.

Figure 26 Retention module

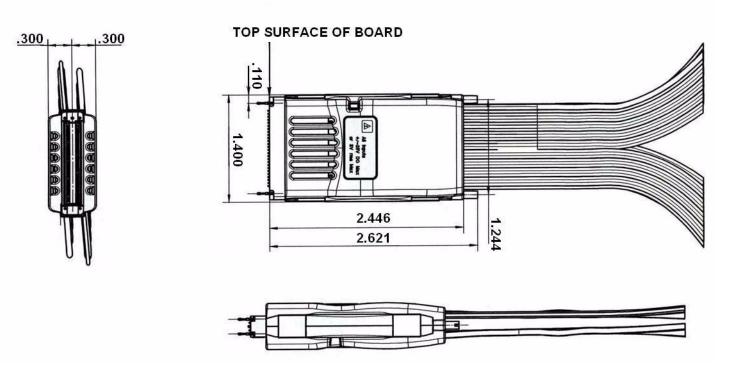

The following figures show the dimensions of the retention module from different views.

Figure 27 Dimensions of the Retention Module and its Parts

Figure 28 Dimensions of the Retention Module and its Parts

Figure 29 Dimensions of the Retention Module and its Parts

Figure 30 Dimensions of the Retention Module and its Parts

Figure 31 Dimensions of the Retention Module and its Parts

Figure 32 Dimensions of the Retention Module and its Parts

Figure 33 Dimensions of the Retention Module and its Parts

Figure 34 Dimensions of the Retention Module and its Parts

#### N5311 Midbus Interposer Card

The N5311 Midbus Interposer card provides the ability to capture the traffic between the two components when footprints are not available.

The following figure displays the dimensions of N5311 in millimeters (mm). The lower connector varies depending on the link width (x1, x4, x8, or x16). Also, the retention module on the right is only available for x16.

Figure 35 N5311 Midbus Interposer

Depending on the type of midbus probe, the N5311 Midbus Interposer card is available in the following flavors:

- For N4241A Midbus Probe:

- N5311-66401 (x1 Midbus Interposer)

- N5311-66404 (x4 Midbus Interposer)

- N5311-66408 (x8 Midbus Interposer)

- N5311-66426 (x16 Midbus Interposer). With this flavor of midbus interposer, maximum two N4241A midbus probes can be connected. This midbus interposer card routes one direction on each retention module.

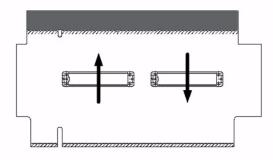

Figure 36 N5311-66426 Midbus Interposer Card

- For N4242A Midbus Probe:

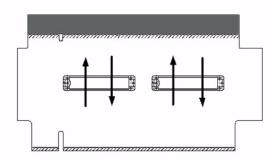

- N5311-66416 (x16 Midbus Interposer). With this flavor of midbus interposer, only one N4242A Probes can be connected. This midbus interposer card routes lane 0 ... 7, bi-directional to the retention module on the left and lane 8...15, bi-directional to the retention module on the right (Figure 10).

# **Electrical Design Considerations for the Midbus 2.0 Probes**

This section contains specific electrical design details of the midbus 2.0 (full size) probes. These specific details include midbus routing suggestions and pin assignments.

These specific electrical design details are in addition to the general electrical design details that apply to all midbus probes (including the N5328A half size midbus probe). The general electrical design details include analyzer eye requirement definition, system impact due to midbus probe presence, and load models. See "Electrical Design Considerations for Midbus Probes" on page 69.

Also, see the electrical design details for the reference clock probe (which is the same for full size and half size midbus probes. See "Reference Clock Probe" on page 72.

The PCI Express Gen2 analyzer offers different probing options for different applications to suit different footprints on the device under test (DUT).

- "Routing considerations near/through PCI Express midbus footprint" on page 51

- "PCI Express Midbus Pin Assignments Overview" on page 52

- "General Probing Option and Pin Assignments" on page 53

- "Straight Probing Option and Pin Assignments" on page 54

- "Swizzled x16 Probing Option and Pin Assignments" on page 57

- "Split x4 Probing Option and Pin Assignments" on page 60

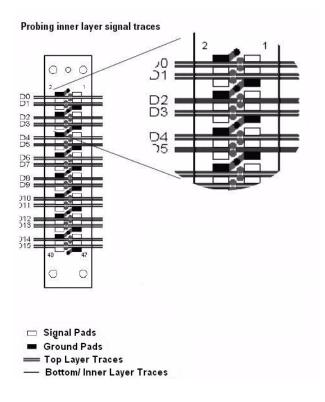

#### Routing considerations near/through PCI Express midbus footprint

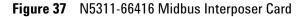

Agilent will provide detailed information on routing and design considerations at a later date. The following figures present suggested routing for footprint negotiation in the case of surface (microstrip) routing when this routing is on the same side of the board as midbus.

Probing top layer signal traces

Figure 38 Suggested routing for microstrip traces on same layer as midbus

#### **PCI Express Midbus Pin Assignments Overview**

There is flexibility in the arrangement and layout of the midbus footprint. Agilent will provide configuration of the midbus to support the following midbus layouts. There is a detailed view of these connections below.

The pinout for the PCI Express midbus is given in "General Probing Option and Pin Assignments" on page 53. It is imperative that designers understand there is some freedom associated with the pin/signal assignment relationship. These notes are given here:

| Footprint channel vs.<br>lane/link<br>designations | <ul> <li>Channel = either an upstream OR downstream differential pair for a given lane</li> <li>C<letter> = the designator for a Channel which accepts a given differential pair of signals</letter></li> <li>C<letter> = the two signals of the differential pair.The signals within a given pair may be assigned to either p or n regardless of polarity</letter></li> </ul>                                                                                                                                                                                         |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General rules for<br>signal pair<br>assignment     | The differential pairs that make up the PCI Express links must be<br>assigned to specific pins of the footprint. However, there is some<br>freedom in this pair assignment in order to minimize routing constraints<br>on the platform. Additionally, note that the channel to footprint<br>assignment configuration is closely related to the "direction" of the<br>probed link. More specifically, a bi-directional pin assignment is different<br>from a unidirectional pin assignment. See the following tables contained<br>in this section for more information. |

# **General Probing Option and Pin Assignments**

| Pin # | Signal Name | Pin # | Signal Name |

|-------|-------------|-------|-------------|

|       |             | G1    | GND         |

| 2     | GND         | 1     | САр         |

| 4     | СВр         | 3     | CAn         |

| 6     | CBn         | 5     | GND         |

| 8     | GND         | 7     | ССр         |

| 10    | CDp         | 9     | CCn         |

| 12    | CDn         | 11    | GND         |

| 14    | GND         | 13    | CEp         |

| 16    | CFp         | 15    | CEn         |

| 18    | CFn         | 17    | GND         |

| 20    | GND         | 19    | CGp         |

| 22    | СНр         | 21    | CGn         |

| 24    | CHn         | 23    | GND         |

| 26    | GND         | 25    | Clp         |

| 28    | CJp         | 27    | CIn         |

| 30    | CJn         | 29    | GND         |

| 32    | GND         | 31    | СКр         |

## Table 1 General PCI Express midbus pinout

| Pin # | Signal Name | Pin # | Signal Name |

|-------|-------------|-------|-------------|

| 34    | CLp         | 33    | CKn         |

| 36    | CLn         | 35    | GND         |

| 38    | GND         | 37    | СМр         |

| 40    | СNр         | 39    | CMn         |

| 42    | CNn         | 41    | GND         |

| 44    | GND         | 43    | СРр         |

| 46    | СОр         | 45    | CPn         |

| 48    | CQn         | 47    | GND         |

| G2    | GND         |       |             |

Table 1

General PCI Express midbus pinout (continued)

#### **Straight Probing Option and Pin Assignments**

This type of probe connects all 16 differential pairs of one probe head to one I/O module. In case of a uni-directional pin configuration it can be used to probe a single direction of a x1...x16 link (see Table 4), and in case of bi-directional configuration it can be used to probe both directions of a x1...x8 link (see Table 5).

#### NOTE

The midbus probe cable comes with two wires: brown and yellow. Out of these wires, only brown cable is supported for applying external clock.

| Pin # | Signal Name | Pin # | Signal Name |  |

|-------|-------------|-------|-------------|--|

|       |             | G1    | GND         |  |

| 2     | GND         | 1     | СОр         |  |

| 4     | C1p         | 3     | COn         |  |

| 6     | C1n         | 5     | GND         |  |

| 8     | GND         | 7     | C2p         |  |

| 10    | СЗр         | 9     | C2n         |  |

| 12    | C3n         | 11    | GND         |  |

| 14    | GND         | 13    | C4p         |  |

| 16    | С5р         | 15    | C4n         |  |

| 18    | C5n         | 17    | GND         |  |

Table 2

x16 (standard) PCI Express midbus pinout<sup>1, 2, 3, 4</sup>

| Pin # | Signal Name | Pin # | Signal Name |

|-------|-------------|-------|-------------|

| 20    | GND         | 19    | Сбр         |

| 22    | C7p         | 21    | C6n         |

| 24    | C7n         | 23    | GND         |

| 26    | GND         | 25    | С8р         |

| 28    | С9р         | 27    | C8n         |

| 30    | C9n         | 29    | GND         |

| 32    | GND         | 31    | C10p        |

| 34    | C11p        | 33    | C10n        |

| 36    | C11n        | 35    | GND         |

| 38    | GND         | 37    | C12p        |

| 40    | C13p        | 39    | C12n        |

| 42    | C13n        | 41    | GND         |

| 44    | GND         | 43    | C14p        |

| 46    | C15p        | 45    | C14n        |

| 48    | C15n        | 47    | GND         |

| G2    | GND         |       |             |

Table 2

x16 (standard) PCI Express midbus pinout<sup>1, 2, 3, 4</sup> (continued)

<sup>1</sup> Polarity (p and n) of each differential pair may be swapped.

$^2$  This configuration can only probe either upstream 16 channels OR 16 downstream channels with one midbus. Please see Table 5 for a configuration that supports interleaved x16 traffic amongst two midbus footprints.

<sup>3</sup> Entire link assignment may be reversed in midbus. For example, channel 0 may be swapped in above table with channel 15, channel 1 with channel 14, etc. If swapping upstream, must also swap downstream (and vice versa).

<sup>4</sup> Analyzer supports probing of one link with smaller link width (x1, x2, x4, x8) on natural lane boundaries, e.g. a x4 link can be probed on lanes 0...3, 4...7, 8...11 or 12...15.

| Table 3 | x8 (straight, bi-directional) specific PCI Express midbus p | pinout <sup>1, 2, 3, 4, 5</sup> |

|---------|-------------------------------------------------------------|---------------------------------|

| Pin # | # Signal Name   |    | Signal Name   |

|-------|-----------------|----|---------------|

|       |                 | G1 | GND           |

| 2     | GND             | 1  | COp- Upstream |

| 4     | C0p- Downstream | 3  | COn- Upstream |

| 6     | COn- Downstream | 5  | GND           |

| 8     | GND             | 7  | C1p- Upstream |

| Pin # | Signal Name     | Pin # | Signal Name   |  |  |

|-------|-----------------|-------|---------------|--|--|

| 10    | C1p- Downstream | 9     | C1n- Upstream |  |  |

| 12    | C1n- Downstream | 11    | GND           |  |  |

| 14    | GND             | 13    | C2p- Upstream |  |  |

| 16    | C2p- Downstream | 15    | C2n- Upstream |  |  |

| 18    | C2n- Downstream | 17    | GND           |  |  |

| 20    | GND             | 19    | C3p- Upstream |  |  |

| 22    | C3p- Downstream | 21    | C3n- Upstream |  |  |

| 24    | C3n- Downstream | 23    | GND           |  |  |

| 26    | GND             | 25    | C4p- Upstream |  |  |

| 28    | C4p- Downstream | 27    | C4n- Upstream |  |  |

| 30    | C4n- Downstream | 29    | GND           |  |  |

| 32    | GND             | 31    | C5p- Upstream |  |  |

| 34    | C5p- Downstream | 33    | C5n- Upstream |  |  |

| 36    | C5n- Downstream | 35    | GND           |  |  |

| 38    | GND             | 37    | C6p- Upstream |  |  |

| 40    | C6p- Downstream | 39    | C6n- Upstream |  |  |

| 42    | C6n- Downstream | 41    | GND           |  |  |

| 44    | GND             | 43    | C7p- Upstream |  |  |

| 46    | C7p- Downstream | 45    | C7n- Upstream |  |  |

| 48    | C7n- Downstream | 47    | GND           |  |  |

| G2    | GND             |       |               |  |  |

Table 3

x8 (straight, bi-directional) specific PCI Express midbus pinout<sup>1, 2, 3, 4, 5</sup>

<sup>1</sup> Polarity (p and n) of each differential pair may be swapped.

<sup>2</sup> Can probe upstream 8 channels AND downstream 8 channels with one midbus.

<sup>3</sup> Entire link assignment may be reversed in midbus. For example, channel 0-upstream may be swapped in above table with channel 7-upstream, channel 1-upstream with channel 6-upstream, etc. If swapping upstream, must also swap downstream (and vice versa).

<sup>4</sup> Upstream and downstream pin assignments may be swapped. For example, channel 0-upstream may be swapped with channel 0-downstream, etc. Note that if one channel of upstream swapped with downstream, all channels upstream and downstream channels must be swapped.

<sup>5</sup> Analyzer supports probing of one bi-directional link with smaller link width (x1, x2, x4) on natural lane boundaries, e.g. a x4 link can be probed on lanes 0...3 or 4...7

#### Swizzled x16 Probing Option and Pin Assignments

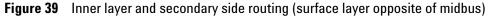

This type of probe is used in cases where a x16 link is split up onto two footprints in such a way that lanes 0...7 of both directions are on one footprint and lanes 8...15 of both directions are on the other. The swizzled probe connects two probe heads to two I/O modules in a way that each of the I/O modules receives all 16 channels of one direction.

The following figure displays a N4242A swizzled x16 midbus probe cable.

Figure 40 N4242A Swizzled x16 Midbus Probe

#### NOTE

The midbus probe cable comes with two wires: brown and yellow. Out of these wires, only brown cable is supported for applying external clock.

The probe heads are labeled Lane 0 ...7, both directions and Lane 8 ...15, both directions. The Lane 0 ...7, both directions probe head must be plugged into the footprint that carries lanes 0...7, whereas the Lane 8 ...15, both directions probe head must be plugged into the footprint that carries lanes 8...15 (Table 6).

# 7 Soft Touch Midbus Probes

| Midbus Footprint for lanes 07 |                 |                                            | Midbus footprint for lanes 815 |             |                  |             |                |

|-------------------------------|-----------------|--------------------------------------------|--------------------------------|-------------|------------------|-------------|----------------|

| Pin<br>#                      | Signal Name     | JamePin<br>#Signal NamePin<br>#Signal Name |                                | Signal Name | Pin<br>#         | Signal Name |                |

|                               |                 | G1                                         | GND                            |             |                  | G1          | GND            |

| 2                             | GND             | 1                                          | COp- Upstream                  | 2           | GND              | 1           | C8p- Upstream  |

| 4                             | C0p- Downstream | 3                                          | COn- Upstream                  | 4           | C8p- Downstream  | 3           | C8n- Upstream  |

| 6                             | COn- Downstream | 5                                          | GND                            | 6           | C8n- Downstream  | 5           | GND            |

| 8                             | GND             | 7                                          | C1p- Upstream                  | 8           | GND              | 7           | C9p- Upstream  |

| 10                            | C1p- Downstream | 9                                          | C1n- Upstream                  | 10          | C9p- Downstream  | 9           | C9n- Upstream  |

| 12                            | C1n- Downstream | 11                                         | GND                            | 12          | C9n- Downstream  | 11          | GND            |

| 14                            | GND             | 13                                         | C2p- Upstream                  | 14          | GND              | 13          | C10p- Upstream |

| 16                            | C2p- Downstream | 15                                         | C2n- Upstream                  | 16          | C10p- Downstream | 15          | C10n- Upstream |

| 18                            | C2n- Downstream | 17                                         | GND                            | 18          | C10n- Downstream | 17          | GND            |

| 20                            | GND             | 19                                         | C3p- Upstream                  | 20          | GND              | 19          | C11p- Upstream |

| 22                            | C3p- Downstream | 21                                         | C3n- Upstream                  | 22          | C11p- Downstream | 21          | C11n- Upstream |

| 24                            | C3n- Downstream | 23                                         | GND                            | 24          | C11n- Downstream | 23          | GND            |

| 26                            | GND             | 25                                         | C4p- Upstream                  | 26          | GND              | 25          | C12p- Upstream |

| 28                            | C4p- Downstream | 27                                         | C4n- Upstream                  | 28          | C12p- Downstream | 27          | C12n- Upstream |

| 30                            | C4n- Downstream | 29                                         | GND                            | 30          | C12n- Downstream | 29          | GND            |

| 32                            | GND             | 31                                         | C5p- Upstream                  | 32          | GND              | 31          | C13p- Upstream |

| 34                            | C5p- Downstream | 33                                         | C5n- Upstream                  | 34          | C13p- Downstream | 33          | C13n- Upstream |

| 36                            | C5n- Downstream | 35                                         | GND                            | 36          | C13n- Downstream | 35          | GND            |

| 38                            | GND             | 37                                         | C6p- Upstream                  | 38          | GND              | 37          | C14p- Upstream |

| 40                            | C6p- Downstream | 39                                         | C6n- Upstream                  | 40          | C14p- Downstream | 39          | C14n- Upstream |

| 42                            | C6n- Downstream | 41                                         | GND                            | 42          | C14n- Downstream | 41          | GND            |

| 44                            | GND             | 43                                         | C7p- Upstream                  | 44          | GND              | 43          | C15p- Upstream |

| 46                            | C7p- Downstream | 45                                         | C7n- Upstream                  | 46          | C15p- Downstream | 45          | C15n- Upstream |

| 48                            | C7n- Downstream | 47                                         | GND                            | 48          | C15n- Downstream | 47          | GND            |

Table 4

Swizzled x16 PCI Express midbus pinout<sup>1, 2, 3, 4, 5</sup>

| Midbus Footprint for lanes 07 |                            |          | Midbus                  |   |          | is footprint for lanes 8 | .15      |             |

|-------------------------------|----------------------------|----------|-------------------------|---|----------|--------------------------|----------|-------------|

| Pin<br>#                      | Signal Name                | Pin<br># | Signal Name             |   | Pin<br># | Signal Name              | Pin<br># | Signal Name |

| G2                            | GND                        |          |                         |   | G2       | GND                      |          |             |

| <sup>1</sup> Pola             | rity (p and n) of each dif | ferentia | al pair may be swapped. | - |          |                          |          |             |

# Table 4 Swizzled x16 PCI Express midbus pinout<sup>1, 2, 3, 4, 5</sup> (continued)

$^{2}$  Can probe upstream 16 channels and downstream 16 channels with swizzled x16 probe.

<sup>3</sup> Entire link assignment may be reversed in midbus. For example, channel 0-upstream may be swapped in above table with channel 7-upstream, channel 1-upstream with channel 6-upstream, etc. If swapping upstream, must also swap downstream (and vice versa) and if swapping footprint A, must also swap footprint B.

<sup>4</sup> Upstream and downstream pin assignments may be swapped. For example, channel 0-upstream may be swapped with channel 0-downstream, etc. Note that if one channel of upstream swapped with downstream, all channels upstream and downstream channels must be swapped.

<sup>5</sup> Analyzer supports probing of one bi-directional link with smaller link width (x1, x2, x4, x8) on natural lane boundaries, e.g. a x4 link can be probed on lanes 0...3, 4...7, 8...11 or 12...15.

| To use the<br>N4242A swizzled |     | g the probe head labeled Lane $0 \dots 7$ , both directions into the ention module carrying lane $0$ to $7$ .                                                                                       |

|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| x16 midbus probe              | In  | the following figure, that is the retention module on the right.                                                                                                                                    |

|                               |     | g the probe head labeled Lane 815, both directions into the ention module carrying lane 8 to 15.                                                                                                    |

|                               |     | the following figure, that is the retention module on the left. Older<br>bes might be labeled B.                                                                                                    |

| NOTE                          | 15, | robes might be labeled A instead of Lane 07, both directions and B instead of Lane<br>both directions. In case you are using a probe marked B, then this probe must be<br>I in 180 degrees rotated. |

#### 7 Soft Touch Midbus Probes

Figure 41 Connecting Swizzled x16 to Retention and I/O Modules

- 3 Plug the module connector labeled Lane 0 ...15, upstream into an N5306A I/O module.

- **4** Plug the module connector labeled Lane 0 ...15, downstream into a different N5306A I/O module.

- **5** In the Protocol Analyzer GUIs for both of the N5306A I/O modules, select the probe type for swizzled probes in the Hardware Setup dialog box.

Remember that one module is now capturing upstream traffic only while the other is capturing downstream traffic only. In order to view both directions in one listing, add both analyzers to a single session.

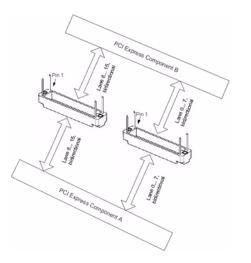

#### **Split x4 Probing Option and Pin Assignments**

This type of probe is used to probe two bi-directional x1...x4 links on the same footprint simultaneously. The split x4 probe connects one probe head to two I/O modules in such a way that each I/O module analyzes one of the bi-directional links (see Table 8).

| Pin # | Signal Name      | Pin # | Signal Name    |

|-------|------------------|-------|----------------|

|       |                  | G1    | GND            |

| 2     | GND              | 1     | C0p- Upstream1 |

| 4     | C0p- Downstream1 | 3     | COn- Upstream1 |

| 6     | C0n- Downstream1 | 5     | GND            |

| 8     | GND              | 7     | C1p- Upstream1 |

| Table 5Dual x4 (bi-directional | I) |

|--------------------------------|----|

|--------------------------------|----|

| Pin # | Signal Name      | Pin # | Signal Name    |

|-------|------------------|-------|----------------|

| 10    | C1p- Downstream1 | 9     | C1n- Upstream1 |

| 12    | C1n- Downstream1 | 11    | GND            |

| 14    | GND              | 13    | C2p- Upstream1 |

| 16    | C2p- Downstream1 | 15    | C2n- Upstream1 |

| 18    | C2n- Downstream1 | 17    | GND            |

| 20    | GND              | 19    | C3p- Upstream1 |

| 22    | C3p- Downstream1 | 21    | C3n- Upstream1 |

| 24    | C3n- Downstream1 | 23    | GND            |

| 26    | GND              | 25    | COp- Upstream2 |

| 28    | C0p- Downstream2 | 27    | COn- Upstream2 |

| 30    | C0n- Downstream2 | 29    | GND            |

| 32    | GND              | 31    | C1p- Upstream2 |

| 34    | C1p- Downstream2 | 33    | C1n- Upstream2 |

| 36    | C1n- Downstream2 | 35    | GND            |

| 38    | GND              | 37    | C2p- Upstream2 |

| 40    | C2p- Downstream2 | 39    | C2n- Upstream2 |

| 42    | C2n- Downstream2 | 41    | GND            |

| 44    | GND              | 43    | C3p- Upstream2 |

| 46    | C3p- Downstream2 | 45    | C3n- Upstream2 |

| 48    | C3n- Downstream2 | 47    | GND            |

| G2    | GND              |       |                |

Table 5

Dual x4 (bi-directional) (continued)

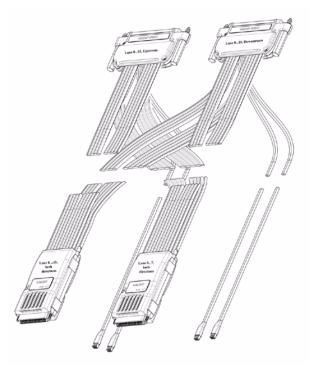

# N5328A Half Size Midbus Probe

- "Setting Up the Probe" on page 64

- "Footprint Pinout of the Probe" on page 64

- "Mechanical Dimensions" on page 65

This chapter provides information on the N5328A half size midbus probe used for PCIe.

There are situations when the space constraints in a board's design prevent having a full sized probe to capture and debug signals. In such situations, the customer compromises and creates a half sized foot print instead. For such situations, Agilent provides the N5328A half size midbus probe, which you can connect to the smaller foot prints to capture the traffic.

The N5328A half size midbus probe supports two different footprints: *straight* and *alternate*.

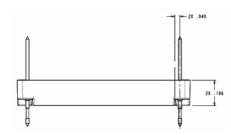

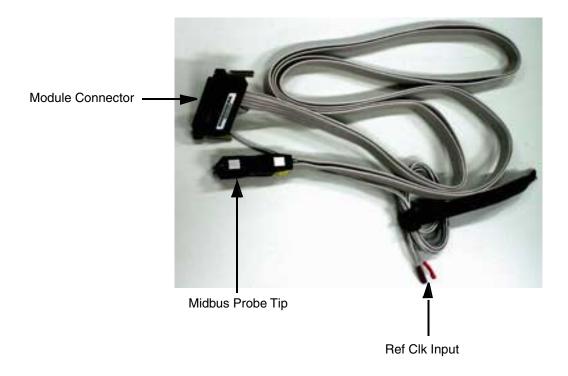

The following figure shows the N5328A half size midbus probe cable.

Figure 42 N5328A Half Size Midbus Probe

Components shown in the above figure are described below:

• **Module Connector**– This component connects to the *Analyzer Probe* component of the N5306A I/O module.

For information on N5306A I/O module, see Chapter 1, "N5306A I/O Module," starting on page 7.

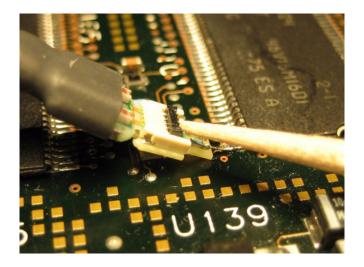

• **Midbus Probe Tip**— This component connects to half size foot print on the board. The following figure shows the midbus probe tip plugged into the retention module for the half size foot print on the backplane board.

Figure 43 Connecting Midbus Probe Tip

**NOTE** For information on retention modules, see Chapter 6, "N5316A Backplane Board for PCIe," starting on page 33.

# WARNING Do not directly touch any component on the N5328A half size midbus probe. It may be hot.

# **CAUTION** Components on the N5328A half size midbus probe are sensitive to the static electricity. Therefore, take necessary anti-static precautions, such as wear a grounded wrist strap, to minimize the possibility of electrostatic damage.

# **Setting Up the Probe**

To setup the probe cable:

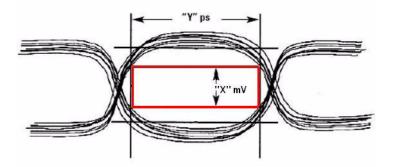

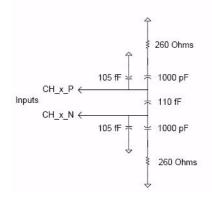

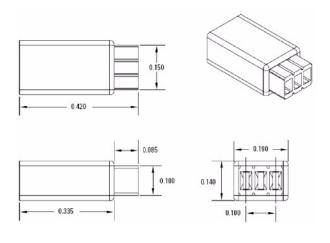

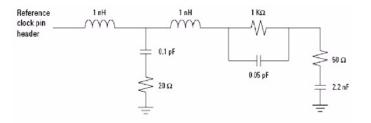

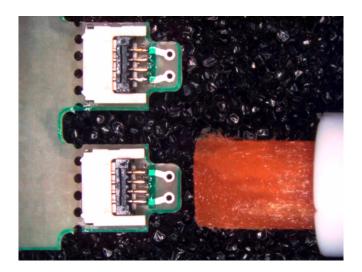

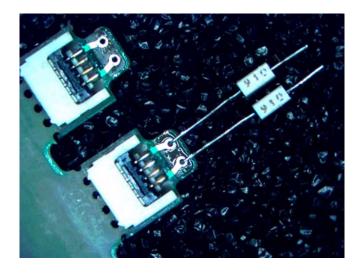

- **1** Solder and secure the retention module on DUT from two sides of the midbus probe footprint.